- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

PIC18F6585/8585/6680/8680

DS30491C-page 180

2004 Microchip Technology Inc.

16.2.4

HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as

outputs to drive push-pull loads. The PWM output signal

is output on the P1A pin while the complementary PWM

output signal is output on the P1B pin (Figure 16-5).

This mode can be used for half-bridge applications, as

shown in Figure 16-6, or for full-bridge applications

where four power switches are being modulated with

two PWM signals.

In Half-Bridge Output mode, the programmable dead-

band delay can be used to prevent shoot-through

current in half-bridge power devices. The value of bits

PDC6:PDC0 sets the number of instruction cycles

before the output is driven active. If the value is greater

than the duty cycle, the corresponding output remains

inactive during the entire cycle. See Section 16.2.6

“Programmable Dead-Band Delay” for more details

of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with

the PORTC<2> and PORTE<6> data latches, the

TRISC<2> and TRISE<6> bits must be cleared to

configure P1A and P1B as outputs.

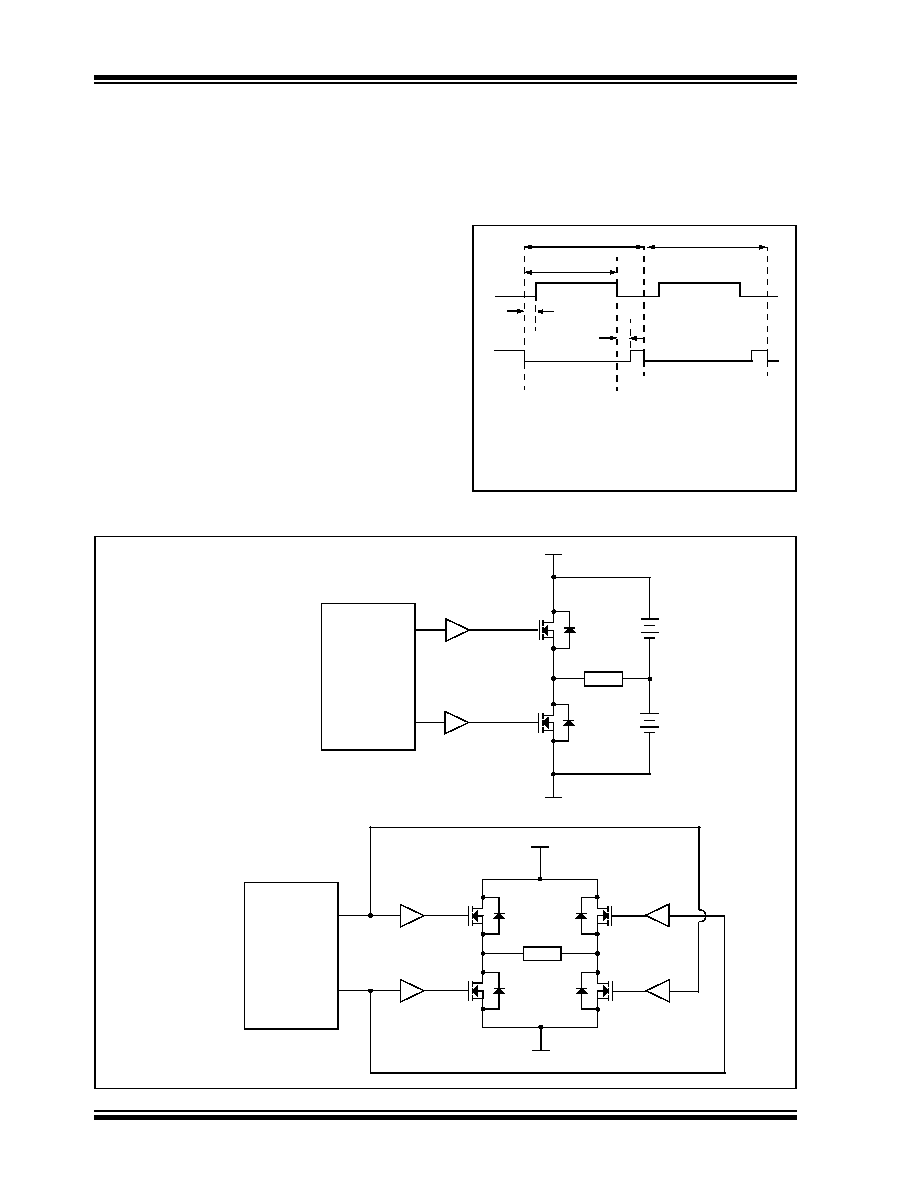

FIGURE 16-5:

HALF-BRIDGE PWM

OUTPUT

FIGURE 16-6:

EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

Period

Duty Cycle

td

(1)

P1A(2)

P1B(2)

td = Dead-band Delay

Period

(1)

Note

1: At this time, the TMR2 register is equal to the

PR2 register.

2: Output signals are shown as active-high.

PIC18FXX80/XX85

P1A

P1B

FET

Driver

FET

Driver

V+

V-

Load

+

V

-

+

V

-

FET

Driver

FET

Driver

V+

V-

Load

FET

Driver

FET

Driver

PIC18FXX80/XX85

P1A

P1B

Standard Half-Bridge Circuit (“Push-Pull”)

Half-Bridge Output Driving a Full-Bridge Circuit

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-2424-11

CONN FPC 24POS 0.5MM SMT

PIC18LF6585T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF6680T-I/PT

IC PIC MCU FLASH 32KX16 64TQFP

XF2J-2224-11

CONN FPC 22POS 0.5MM SMT

PIC18F6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18F4439-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2024-11

CONN FPC 20POS 0.5MM SMT

PIC16LF747-I/ML

IC PIC MCU FLASH 4KX14 44QFN

相关代理商/技术参数

PIC18F85J10-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J10-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-80 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-80

PIC18F85J10T-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048BRAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15T-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J50-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 3936byte RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT